## Sliding mode control of switching converters: general theory in an integrated circuit solution

Alfonso Romero<sup>1,\*</sup>, Luis Martínez-Salamero<sup>1</sup>, Javier Calvente<sup>1</sup>, Eduardo Alarcón<sup>2</sup>, Sonia Porta<sup>3</sup> and Alberto Poveda<sup>2</sup>

<sup>1</sup>Departament d'Enginyeria Electrònica, Elèctrica i Automàtica,

Escola Tècnica Superior d'Enginyeria,

Universitat Rovira i Virgili,

Campus Sescelades, Avda. 26 Països Catalans, 43007 Tarragona, Spain

<sup>2</sup>Departament d'Enginyeria Electrònica,

Universitat Politècnica de Catalunya,

C/ Gran Capità s/n 08024 Barcelona, Spain

<sup>3</sup>Departamento de Ingeniería Eléctrica y Electrónica,

Universidad Pública de Navarra,

Campus de Arrosadía, 31006 Pamplona, Spain

\*Corresponding author: aromero@etse.urv.es

Received 28 February 2005, accepted 1 July 2005

#### Abstract

The application of the sliding-mode control theory to the regulation of dc-to-dc switching converters is reviewed. Subsequently, linear dynamical models are derived and compensating networks are designed. An analog integrated circuit illustrating the theory has been designed, implemented and applied to regulate a buck converter in continuous conduction mode. Experimental verifications are provided.

**Keywords**: Sliding-mode control, compensating networks, integrated circuit controller.

#### 1 Introduction

Use of sliding-mode control techniques in variable structure systems (VSS) renders them very robust regarding to parameter variations and external disturbances. Switching converters constitute an important case of VSS, with several different sliding-mode strategies to control this class of circuits having been reported in the last two decades [1-8]. The design of such strategies is performed in two steps. In the first step, among different sliding surfaces it is selected that one providing the desired asymptotic behavior when the converter dynamics is forced to evolve over it. In the second step, the feedback circuit which addresses the converter dynamics to the sliding surface is designed.

The main advantages of sliding-mode control over conventional PWM control are stability, even for large supply and load variations, robustness, good dynamic response, and simple implementation. However, sliding-mode control presents some drawbacks. First, the switching frequency depends on the working point, due to the control hysteretic nature. Second, steady-state errors can appear in the output response and a significant overshoot in the state variables might arise during the converter transient regime.

There are many commercial integrated circuits for dc-to-dc switching conversion control developed in the last years. Most of them can be chosen from catalogs according to power supply specifications, i.e., input and output voltage levels, converter topology, control strategy, output power, etc. A great number of these circuits perform PWM control in either voltage or current mode with both reference voltage and switching frequency externally adjustable. Another important technique is the PFM regulation which is a variable frequency control that results in low start-up currents, low quiescent currents in the feedback loop, and good efficiency for low output current operation. There are also some integrated controllers that use hysteresis comparators to generate the on/off power transistor control signal. In some cases, the power switch is also integrated in the same controller circuit. Nevertheless, the hysteresis width is fixed in all cases (around 10 mV) and, besides, external signal processing is required to close the control loop. Therefore, if sliding-mode control is implemented through these available hysteresis controllers, some drawbacks will arise, mainly due to the fixed hysteresis width and the need of designing external networks for voltage regulation.

The objective of this paper is to present an analog integrated circuit for sliding-mode control of switching converters. The circuit architecture is derived from the previous work [9] using linear switching surfaces and offers a great versatility to the controller so that it can be used to regulate a large family of switching converters. In Section 2, foundations of sliding-mode control of switching converters are quickly reviewed. Section 3 is devoted to the study of converter dynamical models and the design of compensating networks for specified transient response and reduced steady-state errors. In Section 4, the integrated sliding-mode controller is described. Experimental results are provided in Section 5. Conclusions and some suggestions for further research are given in Section 6.

# 2 Review of sliding-mode control of switching converters

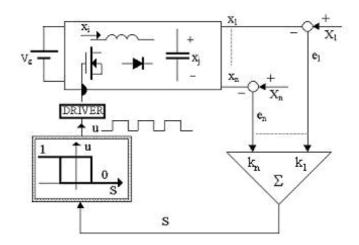

Fig. 1 shows a block diagram of a dc-to-dc switching converter which is controlled by means of a sliding-mode strategy. A hyperplane constitutes the sliding surface whose equation in the state space is expressed by a linear combination of state variable errors  $e_i$ :

$$S = k_1 e_1 + k_2 e_2 + \dots + k_n e_n, \tag{1}$$

$$e_i = X_i - x_i$$

where  $x_1, ...., x_n$  are the *n* state variables of the power converter;  $X_1, ...., X_n$  are their corresponding references and the sliding surface coefficients are represented by  $k_1, ...., k_n$ .

The switch state u is controlled by the hysteretic block, so as to maintain the variable S to be zero.

When the sliding-mode exists, the system dynamics is of (n-1) order. Observe that in sliding-mode S=0, which implies that one state variable in (1) is determined by the rest of variables. The system dynamics is then characterized by S=0, or equivalently by coefficients  $k_1, k_2, ..., k_n$  which are independent of converter parameters.

The existence condition of the sliding-mode requires that all state trajectories near the surface are directed towards it. In mathematical terms this condition is expressed by

$$\lim_{S \to 0^+} \frac{\mathrm{d}S}{\mathrm{dt}} < 0,\tag{2}$$

$$\lim_{S \to 0^{-}} \frac{\mathrm{d}S}{\mathrm{dt}} > 0. \tag{3}$$

Figure 1: Sliding-mode control scheme for a dc-to-dc switching converter

### 3 Compensating networks

In this section the use of compensating networks in sliding-mode switching converters is analyzed. The main goal is the study of linear compensators insertion in the feedback loop in order to achieve usual design specifications of PWM controlled systems for transient-reponse, stability, and steady-state error of the regulated variable [10]. For the system stability survey a linear dynamical model for the converter in the form of a transfer function in the Laplace domain is obtained. Consider again expression (1) in its equivalent form

$$S = k - k_1 e_1 - k_2 e_2 - \dots - k_n e_n \tag{4}$$

where

$$k = \sum_{i=1}^{n} k_i X_i$$

.

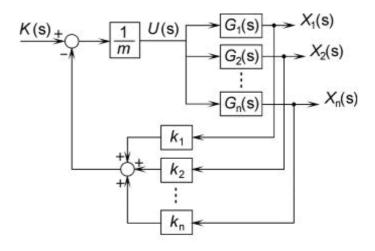

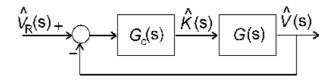

We assume that a correct switching policy applied to u guarantees the fulfilment of conditions (2)-(3) so that a sliding region has been created around the converter equilibrium point. It is also considered that the converter dynamic equations are averaged and linearized and that the open-loop transfer functions relating the control input U(s) and the state variables  $X_1(s), X_2(s), ..., X_n(s)$ , i.e.,  $G_1(s), G_2(s), ..., G_n(s)$ , respectively, are available. Such transfer functions are inserted in the block diagram

of Fig. 2 where the element corresponding to the hysteretic comparator is 1/m. This diagram represents the ideal sliding dynamics when  $m \to 0$ . As the gain 1/m when  $m \neq 0$  can represent the describing function of a PWM modulator, Fig. 2 can be used indistinctly for a PWM design  $(m \neq 0)$  or a sliding-mode design (m = 0).

Figure 2: General block diagram for a dc-to-dc switching regulator using a PWM  $(m \neq 0)$  or sliding-mode (m = 0) controller.

Using Mason's rule, we can obtain the closed-loop transfer functions from the open-loop ones

$$\frac{X_j(s)}{k(s)} = \frac{\frac{1}{m} \cdot G_j(s)}{1 + \frac{1}{m} \cdot \sum_{i=1}^n k_i G_i(s)}.$$

(5)

If  $m \to 0$ , the previous transfer functions correspond to a sliding-mode control. In that case, expression (5) becomes

$$\frac{X_j(s)}{k(s)} = \frac{G_j(s)}{\sum_{i=1}^n k_i G_i(s)}.$$

(6)

The transfer function (6) can be used to analyze stability of the sliding-mode control and also to design a compensating network in order to adjust the value of k in (4) to reach the desired operating point.

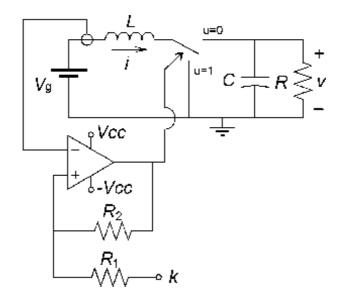

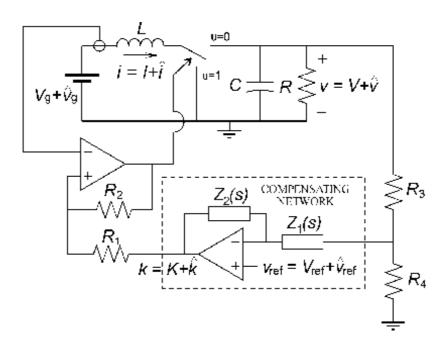

Figure 3: Boost converter with current hysteresis control. (Hysteresis width  $H=2R_1V_{CC}/(R_1+R_2)$ ) .

A sliding-mode controlled boost converter (Fig. 3) will illustrate the procedure.

The converter state equations are the following

$$\frac{di}{dt} = \frac{1}{L} \left[ V_g - (1 - u) \right]$$

$$\frac{dv}{dt} = \frac{1}{C} \left[ i \left( 1 - u \right) - \frac{v}{R} \right]$$

(7)

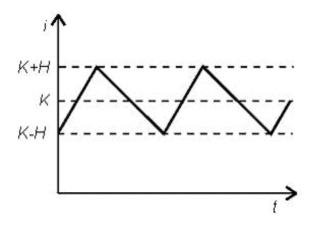

where u = 1 during  $T_{ON}$  and u = 0 during  $T_{OFF}$ . The steady-state behavior of the inductor current i is represented in Fig. 4.

Considering the sliding surface S(x) = K - i, it has been demonstrated [7] that sliding motions exist in the region where

$$V_g < v < \infty. (8)$$

In order to regulate the output voltage v, a compensating network is introduced as shown in Fig. 5, whereas Fig. 6 depicts the block diagram corresponding to the dynamical model of the switching regulator. Here,

Figure 4: Steady-state current behavior.

the superscript ( ) represents, in the Laplace domain, the perturbations superimposed to the equilibrium values which are represented by capital letters  $V_R, K, V$  and  $V_g$ .

The system has been linearized around the equilibrium point, where

$$V = V_R = V_{ref} \cdot \frac{R_3 + R_4}{R_4}.$$

The transfer function relating the output voltage variations to the variations of k is given by expression (6) which results in

$$G(s) = \frac{\hat{V}(s)}{\hat{k}(s)} = \frac{LV_R}{RCV_g} \cdot \frac{\frac{RV_g^2}{LV_R^2} - s}{s + \frac{2}{RC}}.$$

(9)

For the particular choice

$$Z_1(s) = \frac{1}{C_1 s + \frac{1}{R_1}}$$

and  $Z_2(s) = \frac{1}{C_2 s}$ ,

the compensating network corresponds to a PI type whose transfer function  $G_C(s)$  is given by

$$G_C(s) = K_C \cdot \frac{s+z}{s} \tag{10}$$

where  $K_C = \frac{C_1}{C_2}$  and  $z = \frac{1}{R_1 C_1}$ .

The PI design can be simplified if we choose the PI zero so as to cancel the converter pole

$$z = \frac{2}{RC}. (11)$$

With this value for the zero z, the system will be stable if  $K_C$  satisfies the inequality

$$0 < K_C < \frac{V_g RC}{LV_R}. (12)$$

Figure 5: Sliding-mode control of a boost converter with a compensating network for voltage regulation.

Figure 6: Dynamical model of the switching regulator presented in Fig. 5.

The previous analysis is correct as far as the system remains in sliding regime and the ideal sliding dynamics can be considered as a good approximation of the real dynamics. For the first condition, we have to ensure that either the converter initial conditions are on the sliding surface or the system trajectory reaches the surface from zero initial conditions. For the second condition, the hysteresis width H of the comparator must be sufficiently small to assure high switching frequency.

Figure 7: Response of the sliding-mode controlled boost converter of Fig. 3 with a PI compensating network. Upper waveform corresponds to inductor current. Lower waveform corresponds to output voltage.

The sliding-mode controlled boost regulator has been simulated with the following set of parameters:  $V_g=10$  V, R=10  $\Omega$ , L=200  $\mu$ H, C=200  $\mu$ F, and  $V_R=20$  V. The z parameter of the PI is given by expression (11) and the values of  $K_C$  and H have been changed over different simulations. In this case, inequality (12) becomes

$$K_C < 5. (13)$$

Starting with zero initial conditions and with small values for  $K_C$  and H, the state vector rapidly reaches the discontinuity surface and then slides to the equilibrium point. If an input voltage perturbation or a load change is introduced in the system when the converter is in the equilibrium point, the state vector will evolve to a new equilibrium point.

As an example, for  $K_C = 2.5$  and H = 1.5 A, Fig. 7 shows the response of the inductor current and capacitor voltage when the load resistance has a step change from 10 to 20  $\Omega$  at t = 1 ms. Observe that the capacitor voltage recovers the desired output voltage of 20 V at t = 3 ms and exhibits a small overshoot during the transient state. The inductor current, in turn, absorbs the change imposed by the new load requirements. Thus, the state-vector has changed from an initial equilibrium point of I = 4 A, V = 20 V to I = 2 A, V = 20 V, hence preserving the value of the output voltage.

On the other hand, in case of a step perturbation, the increase of  $K_C$  implies a decrease in the transient-state duration. When a certain value of  $K_C$  is reached, the state vector escapes from the sliding surface without returning to it, once the perturbation is introduced into the system.

Small values of H lead to high values of switching frequency and small ripple. If H is increased, the switching frequency will decrease and the ripple will increase.

### 4 Integrated sliding-mode controller

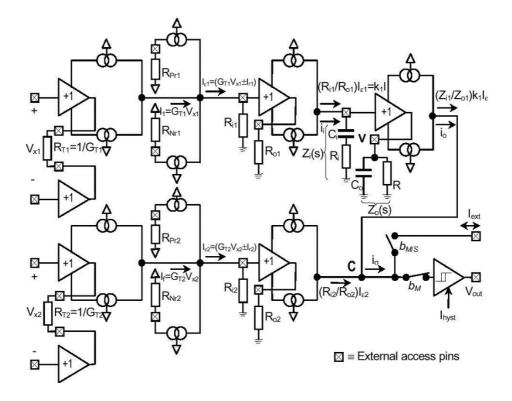

The main blocks of a sliding-mode controller, i.e. a circuit implementing a linear switching surface and a hysteretic comparator, have been integrated in an analog chip. The resulting controller can process two state variables so that expression (1) simplifies to

$$S = k_1(X_1 - x_1) + k_2(X_2 - x_2). (14)$$

Also, compensating networks performing PI, PD or PID filtering action over  $x_1$  have been included in the chip by means of impedances  $Z_1$  and  $Z_2$ . Therefore, expression (14) can be modified as follows

$$S = k_{1P}(X_1 - x_1) + k_{1D} \frac{d(X_1 - x_1)}{dt} + k_{1I} \int_{-\infty}^{t} [X_1 - x_1(\tau)] d\tau + k_2(X_2 - x_2).$$

(15)

Figure 8: Internal architecture of the integrated circuit.

A scheme of the final integrated architecture is shown in Fig. 8 where the triangles represent voltage buffers and the double circle are current mirrors. Signal processing within the chip is performed in current-mode which guarantees high processing speed, easy implementation of mathematical operations, and high noise immunity. The main building block in the chip is a current conveyor (CCII+) whose implementation at transistor level is a class AB complementary source-follower voltage buffer and a complementary regulated cascode current mirror. The final stage in the chip is a current-voltage hysteretic comparator whose hysteresis width can be externally adjusted.

Standard 0.8  $\mu m$  CMOS technology has been used for the implementation of a testchip occupying an area of 0.33 mm<sup>2</sup>. Experimentally measured results from the testchip include low power consumption (1 mA at a switching frequency of 1 MHz), proper CCII+ behavior, and suitability to 3.3 V operation. Details and characteristics of the microelectronic realization of the chip can be found in [9].

#### 5 Experimental results

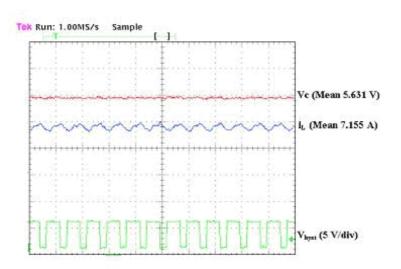

The integrated controller has been tested in a buck converter with the following parameters:  $V_q = 12 \text{ V}$ ,  $L = 220 \mu\text{H}$  and  $C = 100 \mu\text{F}$ .

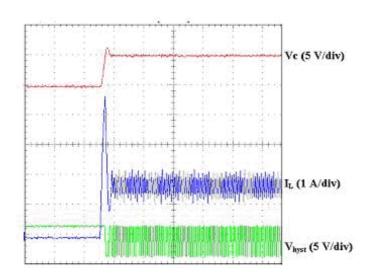

Fig. 9 shows the steady-state waveforms corresponding to capacitor voltage, inductor current, and hysteresis output for a desired equilibrium point of I = 7.15 A, V = 5.6 V (40 W output power) which is obtained by means of the surface

$$S = 1.5 (v - 5.6) + 3 \int_{-\infty}^{t} [v(\tau) - 5.6] d\tau + 1 (i - 7.15),$$

where v is the capacitor voltage and i is the inductor current, and results in a switching frequency of 26 kHz for the considered hysteresis.

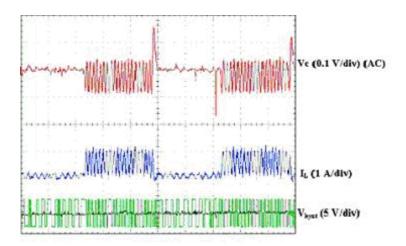

Large-signal operation during start-up is depicted in Fig. 10, which corresponds to the surface

$$S = 4(v - 5) + 1(i - 1.55).$$

After a fast transient state the desired equilibrium point is reached with a resulting switching frequency of 20 kHz.

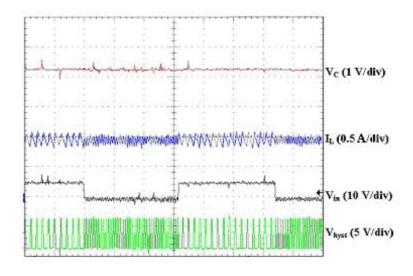

In Fig. 11, the response to a step change in the output load (from 4.4  $\Omega$  to 3.1  $\Omega$  and later from 3.1  $\Omega$  to 4.4  $\Omega$ ) can be observed. The sliding surface selected is

$$S = 4(v - 5.3) + 1(i - 1.2).$$

Notice the steady-state error of around 30 mV in the output voltage for the desired dc value of 5.3 V.

The converter response to periodic step changes in the input voltage can be seen in Fig. 12 for the surface

$$S = 1.5 (v - 4.4) + 1.33 \int_{-\infty}^{t} [v(\tau) - 4.4] d\tau + 1 (i - 1)$$

between 17 and 12 V. Observe that the output voltage has zero steady-state error due to the integral action.

Figure 9: Steady-state waveforms corresponding to surface  $S=1.5~(v-5.6)+3\int_{-\infty}^{t}\left[v\left(\tau\right)-5.6\right]\,d\tau+1\left(i-7.15\right).$

Figure 10: Start-up response corresponding to surface  $S=4\ (v-5)+1\ (i-1.55)$  .

Figure 11: Converter response corresponding to surface  $S=4\ (v-5.3)+1\ (i-1.2)$  and step change in the load resistance.

Figure 12: Converter response corresponding to surface  $S=1.5~(v-4.4)+1.33\int_{-\infty}^{t}\left[v\left(\tau\right)-4.4\right]~d\tau+1~(i-1)$ and step changes in the input voltage.

#### 6 Conclusions

The main elements of the sliding-mode control theory for switching converters regulation have been analyzed in this paper. The results of static and dynamic analyses of the switching converter under sliding-mode control have been employed in the design of an integrated controller implemented in  $0.8~\mu m$  CMOS technology using current-mode circuit techniques. As a result, the converter transient-state behavior can be controlled by allowing simultaneously a fast response and a low overshoot. Zero steady state voltage error can be also obtained when the integral function is activated in the compensating network of the chip.

Future work contemplates the application of this chip in the regulation of other converters such as boost, buck-boost, Cuck, SEPIC, etc and also the realization of new microelectronic designs integrating both power switch and driver.

This work has been sponsored by the Spanish Ministry of Science and Technology under grant TIC2001-2157-C02.

#### References

- [1] V.I. Utkin, Sliding Modes and Their Application in Variable Structure Systems (Mir, Moscow, 1974).

- [2] U. Itkis, Control Systems of Variable Structure (Wiley, N.Y., 1976).

- [3] F. Bilalovic, O. Music, and A. Sabanovic, Proc. PCI'83, p.331 (1983).

- [4] R. Venkatamaran, Sliding mode control of power converters, Ph. D. Dissertation, Calif. Inst. Technol., Pasadena, 1986.

- [5] R. Venkatamaran, A. Sabanovic and S. Čuk, Proc. IECON'85, p. 251 (1985).

- [6] S. Sanders, G.C. Verghese and D.F. Cameron, Proc. 25th Conf. Decision Contr., p. 46 (1986).

- [7] H. Sira-Ramírez, IEEE Trans. Circuits and Systems 34, 919 (1987).

- [8] L. Martínez-Salamero, J. Calvente, R. Giral, A. Poveda, and E. Fossas, IEEE Trans. Circuits and Systems 45, 355 (1998)

- [9] E. Alarcón, A. Romero, A. Poveda, S. Porta, and L. Martínez-Salamero, Electronics Letters **38**, 104 (2002).

- [10] R. Giral, L. Martínez-Salamero, J. Hernanz, J. Calvente, F. Guinjoan, A. Poveda, and R. Leyva, Proc. ISCAS'95, v.3, p.2055 (1995).